이번 Verilog 두번째 포스트도 이론적인 부분을 좀 살펴볼텐데요.

조합회로(Combinational Logic)과 순차회로(Sequential Logic)에 대한 내용과

동기식(Synchronous), 비동기식(Non-Synchronous)에 대한 내용이 되겠습니다.

이 부분을 잘 파악해야 Verilog를 이용해 무언가를 설계할 때, 생각하면서 코드를 작성할 수 있기 때문에 정리해봤습니다.

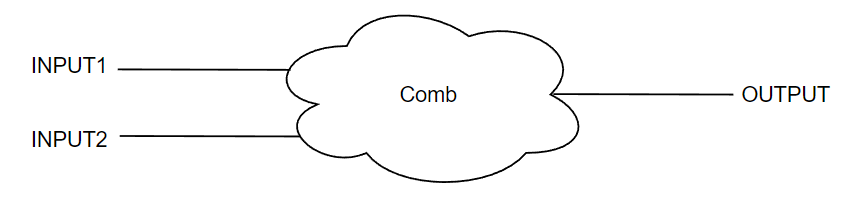

- 조합회로(Combinational Logic)

조합회로는 일정시점의 출력값이 일정시점의 입력값에 의해서만 결정되는 논리회로입니다.

예를 들어 위의 Combinational Logic이 무엇인지는 모르지만 AND Gate라고 했을 때,

당연히 INPUT1, INPUT2가 모두 1이 될 때, 1이라는 OUTPUT이 나오겠죠.

방금 이 과정에서 OUTPUT에 영향을 주는 요소를 생각해보면

현재 들어오는 INPUT 이외에 과거에 저장해놨던 값과 같은 다른 요소가 전혀 없었습니다.

즉, 현재 어떤 값을 Input으로 하여 내부 Logic을 거치게 되면 그에 상응하는 Output이 나오게 된다는 의미입니다.

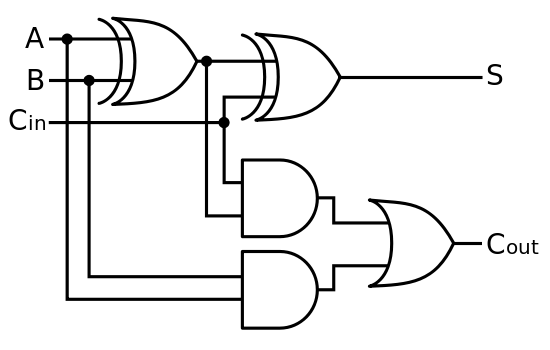

이런 Combinational Logic은 우리가 알고 있는 AND, OR, XOR, NOT 등등의 논리 게이트가 조합되어 구성되어 있다고 생각할 수 있는데 대표적인 예시로 Half-Adder나 Full-Adder, Comparator 등등 수많은 회로가 있으니 참고하셔도 좋을 것 같습니다.

- 순차회로(Sequential Logic)

순차회로는 조합회로와 달리 저장되어 있는 과거 상태의 값과 현재 입력 값에 의해서 현재 출력값이 결정되는 회로입니다.

쉽게 말하자면 조합회로에 기억기능이 추가된 회로라고 생각할 수도 있는데요.

당연히 기억기능이 필요하기에 D Flip-Flop이나 Latch같은 기억회로들이 필요합니다.

위처럼 Combinational Logic을 거쳐서 Register A라는 기억 소자에 저장이 되고

Register A에 저장되어 있는 값이 다시 다른 Combinational Logic을 거쳐 Register B라는 기억소자에 저장되는 등의 과정을 반복하는 회로라고 할 수 있습니다.

기억소자인 Register는 Combination Logic을 거쳐온 결과라던지 과거의 입력이라던지 등의 과거의 어떤 값을 기억하고 있는 녀석들이죠.

즉, Register에 저장된 이 값들과 현재의 Input을 이용해서 Output을 결정하는 회로가 바로 순차회로입니다.

사실 Verilog를 이용해 보통 reg2reg(Register to Register) 방식으로 코드를 작성하기 때문에

가장 자주 보이고 자주 쓰이는 구조가 바로 이 순차회로인 것 같습니다.

조합회로와 순차회로에 대해 알아봤고 이제 동기식과 비동기식에 대해서 정리해보도록 할게요.

동기식(Synchronous), 비동기식(Non-Synchronous)는 사실 기본적인 내용이고 잘 알테니 짧게 써보도록 하겠습니다.

- 동기식(Synchronous)

디지털 회로에는 Clock이라는 것이 존재하죠.

일반적으로 이 Clock신호(일반적으로 Clock의 상승 Edge)에 맞춰 회로의 각 Signal들이 동작하게 하는 것이 일반적입니다.

즉, 이를 Clock에 동기화되어있다고 하고 이를 동기식(Synchronous)이라고 해요.

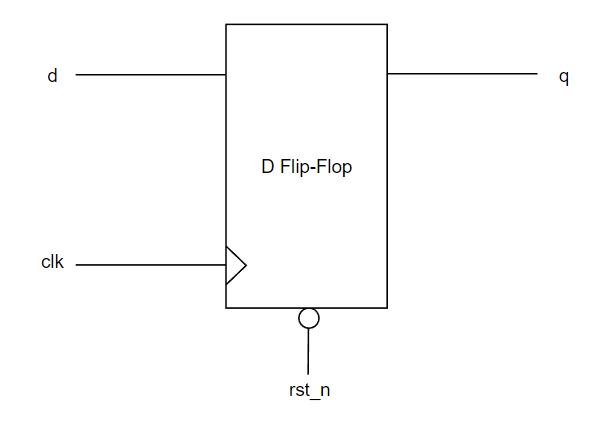

Verilog로 작성한 간단한 D flip-flop 예시를 보면서 살펴보도록 하죠.

D Flip-Flop은 Input으로 clk, d, rst_n이 있고 Output으로 q가 존재합니다.

동작으로는 d에 Input이 들어오게 되면 값을 저장하고 있다가

Clock의 상승 Edge에 맞춰서 q로 내보내주는 간단한 회로입니다.

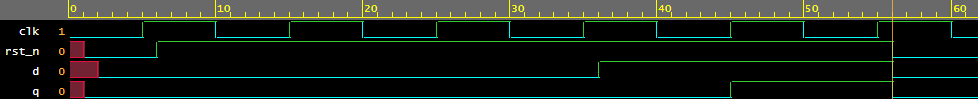

Input data, d가 위의 시점에서 들어왔지만 들어온 시점에 바로 Output data, q로 반영이 되지 않고 있죠.

바로 이렇게 clock의 상승 Edge에 Output data, q에 반영이 되는 방식으로

Clock에 동기화되어 움직이는 모습을 확인할 수 있습니다.

- 비동기식(Non-Synchronous)

반대로 비동기식을 살펴볼까요?

비동기식은 Clock신호와 무관하게 동작을 한다는 의미로

동기식과 다르게 Clock 신호의 상승 Edge를 기다리지 않고 즉시 동작하게 됩니다.

D Flip-Flop에 존재하는 Reset핀은 대표적인 비동기 신호인데요.

동기식에서 살펴봤던 것처럼 한번 살펴보겠습니다.

reset을 시켜주는 즉시 Input data, d와 Output data q가 모두 LOW로 깔리는 것을 확인할 수 있습니다.

즉, Clock신호와 무관하게 동작을 한다는 것을 알 수가 있습니다.

이번 포스트에서는 Verilog 설계 시 필요한 기본적인 개념들에 대해 살펴봤고

다음 포스트부터는 실제로 Verilog 설계와 관련된 내용으로 돌아오도록 할게요 :)

최근댓글