사실 Verilog에 대한 포스트를 블로그 시작할 때, 우선적으로 쓰려고 했는데 이제서야 쓰게 되네요.

앞으로 Verilog 카테고리에 Verilog에 대해서 공부했던 내용들과 간단하게 구현했던 내용들을 정리해보도록 하겠습니다 :)

이번 포스트에서는 Verilog에 대해서 간단히 Intro 수준으로 살펴보고 마치도록 할게요.

먼저, 베릴로그는 Digital System을 Describe하기 위한 하드웨어기술언어(HDL)입니다.

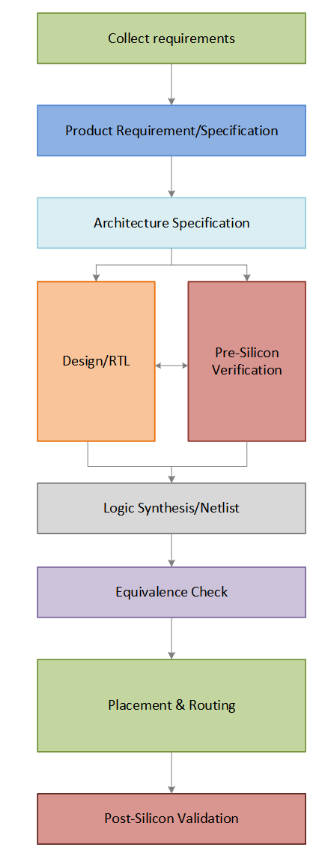

Chip 설계 흐름에서 본다면 소프트웨어와 달리 하드웨어를 기술하는 언어인 베릴로그를 이용해 RTL Code를 짜게되면

이후 합성을 통해 Gate 논리 회로로 표현이 되고

이후 Timing/Equivalence Check, Phsycal 적인 Cell 배치를 하는 P&R, 실제 공정을 통해서 물리적인 Chip이 탄생하게 됩니다.

즉, 컴퓨터 언어같은 베릴로그를 이용해서 회로의 동작, 신호의 흐름을 기술한 코드를 짜게되면

여러 과정을 거쳐 실제 Hardware가 탄생하기에 베릴로그는 하드웨어기술언어(HDL)라 불립니다.

- 추상화(Abstratction Layer) 방식

베릴로그는 총 3가지의 추상화 방식으로 구별을 할 수가 있다고 하는데 이에 대해서 잠깐 살펴봅시다.

-Behavioral level(High Level)

Behavioral Level은 알고리즘 수준에서 시스템을 묘사하는 Level입니다.

하드웨어 내부가 어떻게 구현되는지에 집중하기 보다는 계획한 알고리즘대로 동작을 하는지에 집중하는 Level입니다.

-Register Transfer Level

Register Transfer Level은 흔히 말하는 RTL이죠.

RTL Level에서 구현한다는 것은 회로의 특징과 레지스터 사이의 데이터 전달을 정확히 묘사한다는 의미입니다.

- Gate Level(Low Level)

Gate Level은 미리 정의된 AND, OR, NOT과 같은 Logic들을 연결하고 타이밍 정보를 이용해서 묘사하는 Level입니다.

- Design Style

Verilog를 이용해 하드웨어를 설계하는 Style은 크게 Bottom-Up과 Top-Down, 2가지로 구분할 수가 있습니다.

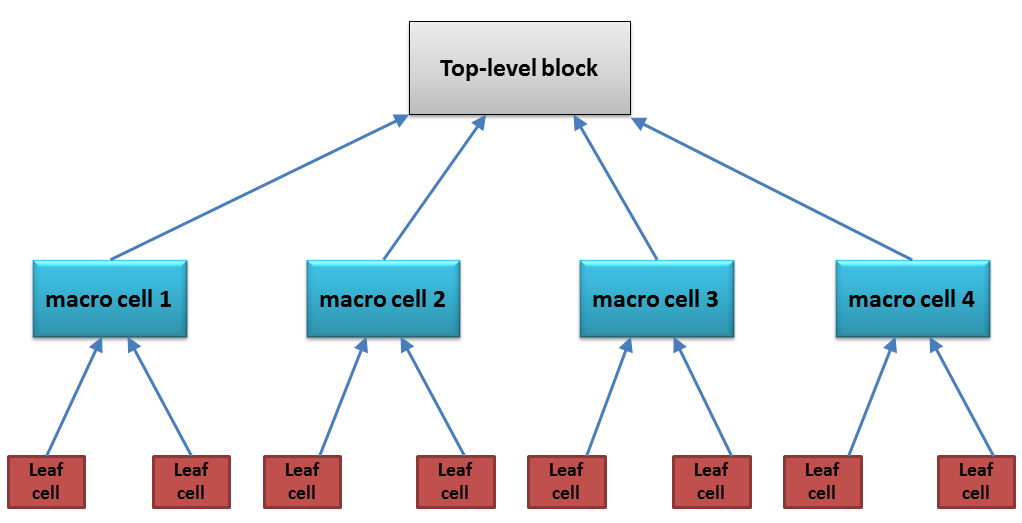

1. Bottom-Up Design

Bottom-Up 방식은 말그대로 아래에서 위로 올라가는 방식으로 작은 부분부터 설계해 나가는 방식으로 회로 Design의 전통적인 방법이라고 합니다.

과거 회로 Design의 복잡도가 심하지 않을 때는 Standard Gate를 활용해 Gate-Level에서 Bottom-Up 방식으로 설계가 진행되었지만 회로 Design 복잡도가 올라감에 따라 Bottom-Up 방식 만으로는 설계가 불가능하다고 합니다.

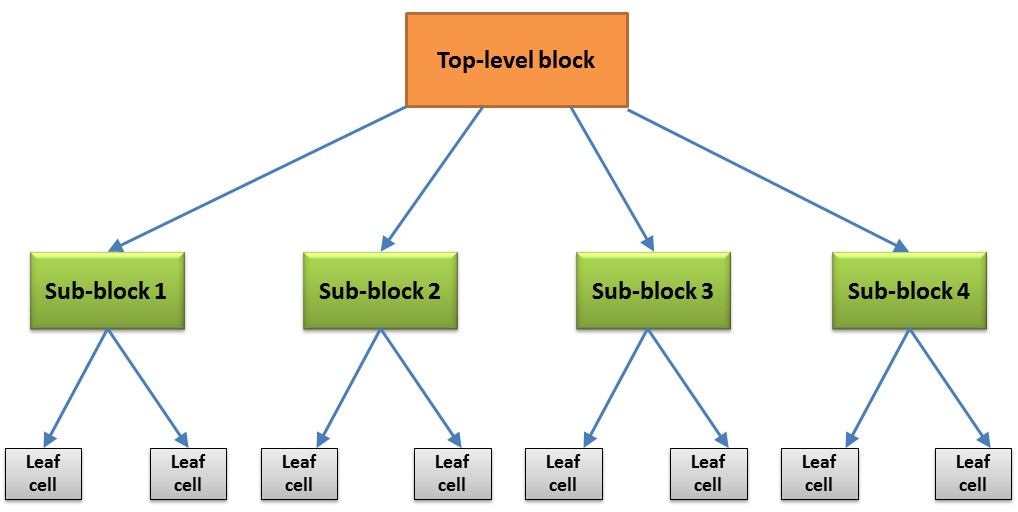

2. Top-Down Design

Top-Down 방식은 Bottom-Up 방식과는 반대로 Top(High)-Level부터 하위로 설계해 나가는 방식입니다.

빠른 테스트나 구조화된 시스템 설계를 가능하게 하는 등 이점이 있지만 Pure Top-Down 방식으로 설계하는 것은 매우 어렵다고 합니다.

이와 같이 Pure Bottom-Up, Pure Top-Down 방식 모두 어려움이 있기때문에 일반적으로 Bottom-Up 방식와 Top-Down 방식을 혼용하여 설계한다고 하네요.

이번 포스트는 이로 간단히 마치고 다음 포스트부터는 실제 Verilog를 이용한 코드 작성에 대해서 한번 살펴보도록 할게요.

출처 :

http://www.vlsifacts.com/digital-design-methodologies/

https://www.chipverify.com/verilog/asic-soc-chip-design-flow

최근댓글