이번 포스트에서는 Verilog 코드 작성 관련해 앞서 설명하지 못했었던 부분들을 좀 모아서 정리해보려고 합니다.

바로 정리해볼게요.

- 벡터

module example(

input wire [3:0] a,

input wire [3:0] b,

output reg [7:0] result

);a나 b, result 앞에 대괄호로 표현된 부분들은 굳이 설명을 하지 않고 계속 사용을 해왔었는데요.

당연히 아시겠지만 Vector로 Verilog에서는 bit크기로 이해하실 수 있습니다.

이는 [데이터타입][[최상위 비트 : 최하위 비트]][변수명] 꼴로 선언하면 되고 위의 예시에서는

4-bit짜리 a, 4-bit짜리 b input과 8-bit짜리 result output을 선언한 것이죠.

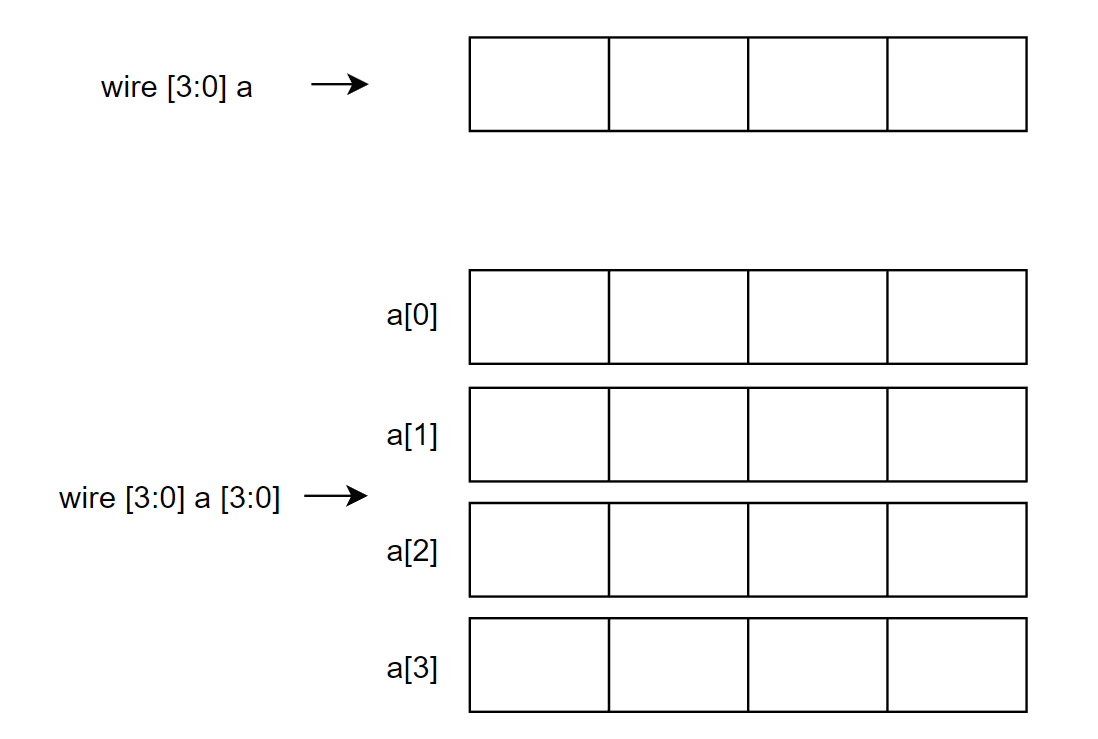

- 배열

module example(

input wire [3:0] a [3:0],

input wire [3:0] b [3:0],

output reg [7:0] result

);배열 같은 경우는 변수명 뒤에 배열 범위를 지정하게 됩니다.

[데이터 타입][변수명][배열 범위] 꼴로 선언하게 되는 것이죠.

위의 예시처럼 선언하게 되면 4-bit짜리 a가 a[0], a[1], a[2], a[3]으로 4개가 생성이 되는 것이죠.

그림으로 표현해보면 이와 같이 생성이 되는 것이겠네요.

- 숫자표현

숫자 표현과 관련해서 binary, decimal, hexadecimal이 존재하는데

숫자를 쓸 때는 숫자의 비트수와 사용할 진수, 숫자를 [비트 수]'[진수] [숫자]꼴로 입력하여 사용하면 됩니다.

참고로 긴 숫자(ex. 101111101100)를 쓸 때, 보기가 힘든 경우가 있는데

이럴 때는 가독성을 위해서 중간중간에 _를 붙여주게 되면(ex. 1011_1110_1100)

숫자에는 영향이 가지않고 가독성을 높일 수가 있습니다.

a = 4'b1111; //binary

b = 4'd15; //decimal

c = 4'hF; //hexdecimal

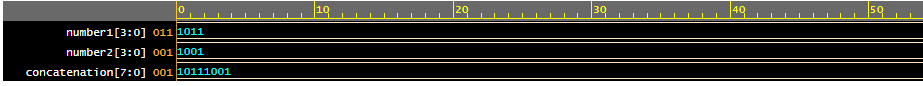

- Concatenation

Concatenation은 어떤 두 수를 연결시켜 주는 연산자라고 할 수 있습니다.

{[number1], [number2]} 꼴로 이렇게 중괄호와 콤마를 이용해서 써주게 되면 두 수가 줄줄이 연결되어 나타나게 됩니다.

한번 4-bit짜리 1011과 4-bit짜리 1001을 연결해서 8-bit짜리 1011_1001를 만들어봅시다.

module conc(

input wire [3:0] number1,

input wire [3:0] number2,

output reg [7:0] concatenation

);

always @(*) begin

concatenation = {number1, number2};

end

endmodule위와 같이 코드를 작성해서 number1에 1011, number2에 1001을 넣어보면

두 수가 이어진 1011_1001이 나타나는 것을 확인할 수 있습니다 :)

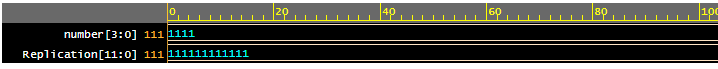

- Replication

Concatenation과 비슷하게 Replication이라는 것도 존재하는데요.

Replication는 특정 숫자를 여러번 반복해서 연결해줍니다.

{반복횟수{number}} 꼴로 작성을 해주면 number가 반복횟수만큼 이어져서 나오게 되는 것이죠.

1111을 3번 반복해서 연결해볼까요?

module repl(

input wire [3:0] number,

output reg [11:0] Replication

);

always @(*) begin

Replication = {3{number}};

end

endmodule위와 같은 코드에서 number를 1111로 넣고 결과를 보게되면

1111이 3번 이어져서 1111_1111_1111로 나오는 것을 확인할 수 있습니다.

최근댓글