지난번 Cortex-M7 Register 포스트에서 General Purpose Register, 범용 레지스터에 대해서 살펴봤었는데

이번 포스트에서는 Special Register에 대해 살펴보도록 하겠습니다.

- Special Register

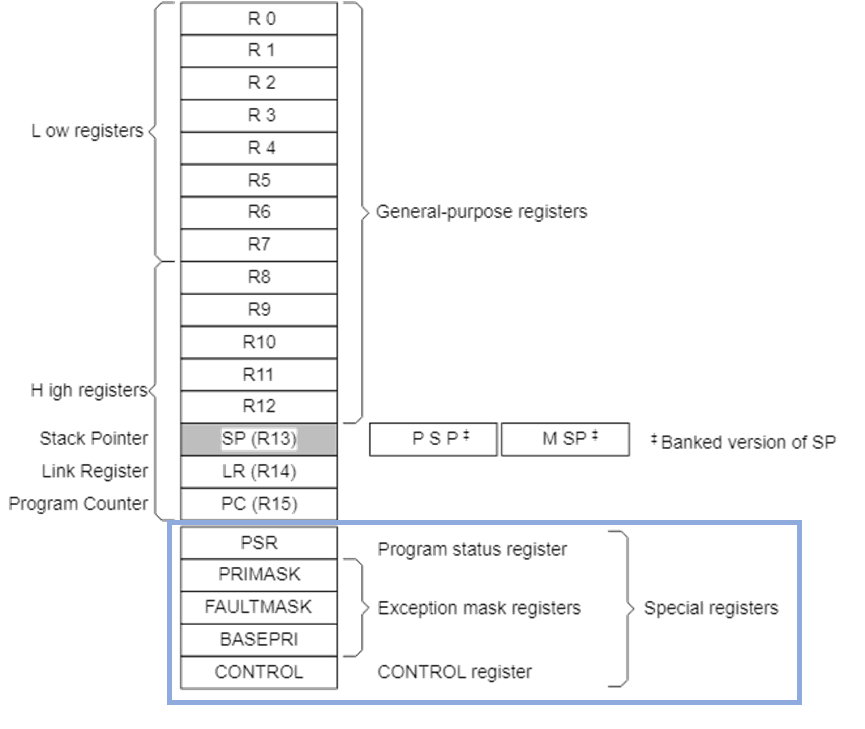

지난번에 봤던 Register File 아래에 Special Register라는 부분이 생겼습니다.

지난번 포스트에서 R0~R12는 Core가 내부적으로 업무를 처리할 때 사용하는 General Register라고 배웠었죠.

이는 Core가 연산에 필요하다면 R0~R12같은 General Register를 쓰고 지울 수 있는 일반적인 목적의 레지스터라는 의미였습니다.

반대로 Special Register는 이름 그대로 Core가 함부로 사용하는 것이 아닌 어떤 특수한 목적을 지닌 Register입니다.

그림에서 보이는 Special Register로 PSR, PRIMASK 등등이 보이는데 하나씩 살펴보겠습니다.

- PSR(Program Status Register)

첫번째로 PSR먼저 살펴보죠.

PSR은 Program Status Register로 Program 상태를 나타내는 Register입니다.

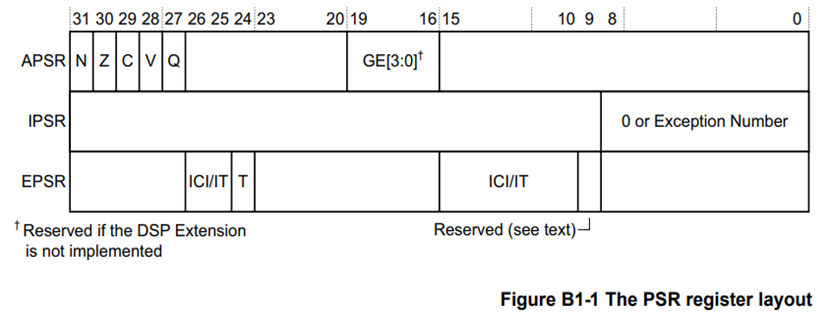

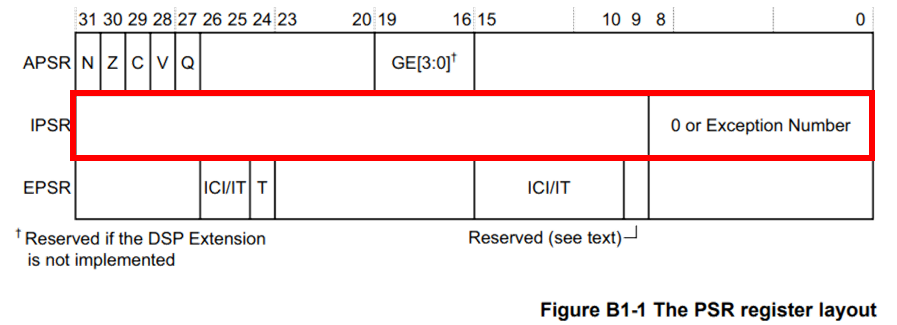

위 Register Layout에서 볼 수 있듯이 PSR은 3개의 Sub-Register(APSR, IPSR,EPSR)를 포함한 32-bit Register입니다.

그럼 각각의 Sub-Register에 대해서 파악한다면 PSR에 대한 내용은 끝이겠네요.

1. APSR(Application Program Status Register)

APSR은 현재 실행하고 있는 프로그램의 상태 정보를 담고 있어요. 각 비트들에 대해서 정리하고 넘어가봅시다.

· N, bit[31]

Negative condition code flag

연산결과가 Negative 즉, 음수라면 이 비트는 1, 아니라면 0입니다.

· Z, bit[30]

Zero condition code flag

연산결과가 Zero 즉, 0이라면 이 비트는 1, 아니라면 0입니다.

· C, bit[29]

Carry condition code flag

Unsigned Overflow on an addition와 같은 Carry가 발생했을 경우 이 비트는 1, 아니라면 0입니다.

· V, bit[28]

Overflow condition code flag

Signed Overflow on an addition와 같은 Overflow가 발생했을 경우 이 비트는 1, 아니라면 0입니다.

· Q, bit[27]

Sticky Saturation Flag

이 bit는 정확히 이해하진 못했지만 특정 Multiply Instructions을 수행 중에 Overflow가 발생하면 Q bit가 1이 된다고 합니다.

예를 들어, 3번의 Multiple 연산을 하는 Instruction을 사용했는데 2번째 연산에서 Overflow가 발생했다면

Overflow가 발생한 2번째 연산과정에서만 Q bit가 1이 됐다가 0으로 Clear되는 것이 아니라

모든 Multiple 연산이 끝날 때까지 Q bit을 1로 유지한다는 것으로 이해했어요.

끈적한이라는 의미를 갖는 Sticky라는 네이밍을 사용한 것도 이 의미지 않을까 생각되네요 :)

· GE, bits[19:16]

Greater than or Equal Flag

SIMD instructions이 individual bytes or halfwords of the operation으로부터의 결과를 나타내기 위해

GE Flag를 사용한다고 하는데 이 부분은 잘 모르겠습니다..

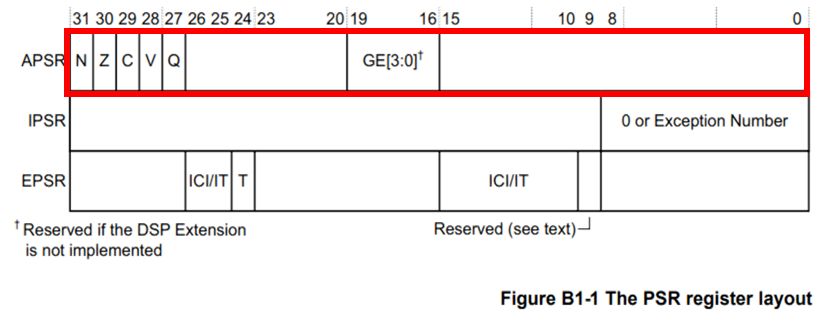

※ C Flag vs V Flag

Carry를 나타내는 C bit와 Overflow를 나타내는 V bit가 헷갈리기도 하고

두 Flag의 정확한 차이가 궁금해서 차이에 대해 좀 정리해볼게요.

이진수를 표현할 때, 음수/양수를 표현하는 Signed System과 부호가 없는 Unsigned System이 존재하죠.

예를 들어, 이진수로 1011이라는 4-bit 수가 있을 때

Unsigned System에서는 이를 10진수로 11로 인식되지만

Signed System에서는 최상단 비트가 1이면 음수를 표현하는 것이므로 10진수로 본다면 -5가 되죠.

따라서 Unsigned System 같은 경우, 4-bit 이진수로 0부터 15까지 표현할 수 있지만

Signed System의 경우 최상단 비트가 부호를 표시하기 때문에 -8부터 7까지 표현할 수 있습니다.

근데 C, V Flag와 이런 Signed/UnSigend System이 무슨 상관이냐의 결론을 말하자면

APSR을 설명하면서

C는 Unsigned Overflow를 나타내고 V는 Signed Overflow를 나타낸다는 Definition이 있었습니다.

즉, Unsigned System에서 표현할 수 있는 수를 넘겼을 때(Unsigned Overflow) C Flag가 1이되고

Signed System에서 표현할 수 있는 수를 넘겼을 때(Signed Overflow) V Flag가 1이 된다고 보면 되겠습니다.

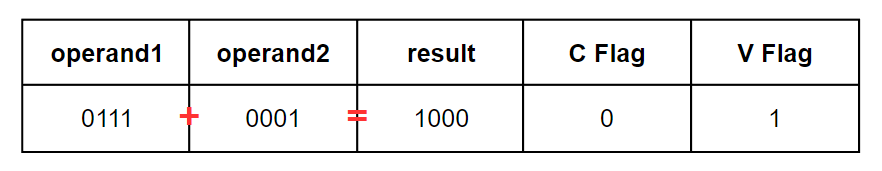

위의 내용을 참고해서 아래와 같은 예시를 봅시다.

0111+0001 연산을 통해 1000이라는 결과가 나온 것은 당연히 아실 수가 있을 겁니다.

그럼 위의 경우를 Un-Signed와 Signed System으로 나누어 살펴볼까요?

1) 설계자가 Unsigned System으로 설계를 진행한 경우, 0111(7) + 0001(1) = 1000(8) 이겠죠.

즉, 연산결과가 Unsigned 4-bit으로 표현할 수 있는 범위(0~15)를 넘기지 않았습니다.

따라서 당연히 C Flag는 0이죠. 그런데 V Flag는 1이네요.

이거는 Signed System의 경우로 봅시다.

2) 설계자가 Signed System으로 설계를 진행한 경우, 0111(7) + 0001(1) = 1000(-8) 입니다.

앞에서 설명했듯 Signed System에서 4-bit로 표현할 수 있는 -8부터 7입니다.

즉, 설계자가 Signed System을 채택하고 위와 같은 연산을 진행했을 때 8을 표현해야하는데

이는 4-bit Signed로 표현할 수 있는 범위를 넘어가기 때문에 Overflow가 발생한거죠.

따라서 V Flag가 1이 됩니다.

정리를 해보자면 Singed냐 Unsigned냐에 따라 볼 Flag가 다르다고 보면 되겠습니다.

만약 자신이 Unsigned System을 고려해 설계했다면 C Flag만 보면서 Unsigned Overflow가 발생했는지 보면 됩니다.

Unsigned System으로 설계했는데 Signed Overflow를 나타내는 V Flag는 당연히 볼 필요가 없겠죠.

반대로 자신이 Signed Sytem을 고려해 설계했다면 Signed Overflow를 나타내는 V Flag만 보면 되겠네요.

2. IPSR(Interrupt Program Status Register)

IPSR은 현재 Handler Mode에서 처리중인 Exception의 Exception Number를 저장하는 레지스터입니다.

Thread Mode에서 일반적인 프로그램을 수행하다가 이런 일반적인 흐름에서 벗어난 일(Exception)이 발생했을 때,

이를 처리하기 위해 Handler Mode로 넘어가게 되죠.

이때, Handler Mode에서 어떤 Exception을 처리하고 있는지에 대해 적어놓는 레지스터라고 볼 수 있습니다.

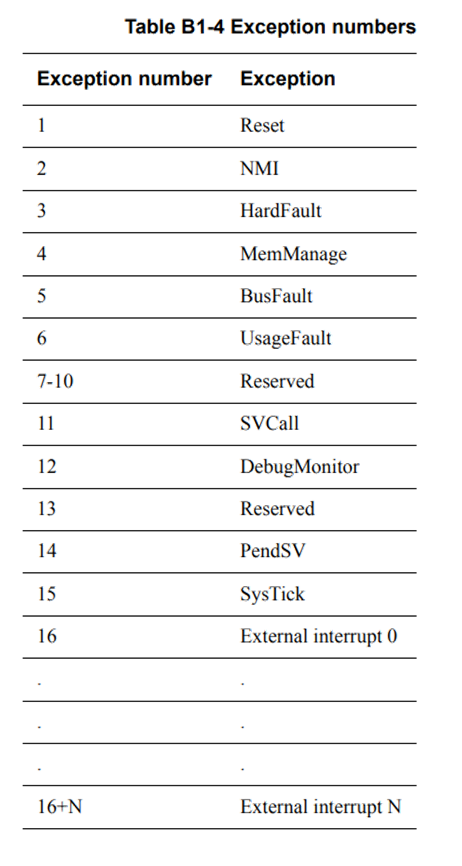

Exception Number는 Cortex Component Block을 설명할 때 등장한 적이 있는데

왼쪽과 같이 각 Exception마다 정해진 Number가 있습니다.

즉, IPSR의 8-bit공간에는 1부터 256까지의 Exception Number 중

처리중인 Exception에 해당하는 Number가 들어가게 되겠죠.

3. EPSR(Execution Program Status Register)

· T, bit[24]

Processor가 Thumb instruction을 실행할 때 이 bit는 1, 아니라면 0입니다.

Cortex-M7의 경우, Thumb-2 Instruction만을 지원하기 때문에 이 bit는 항상 1입니다.

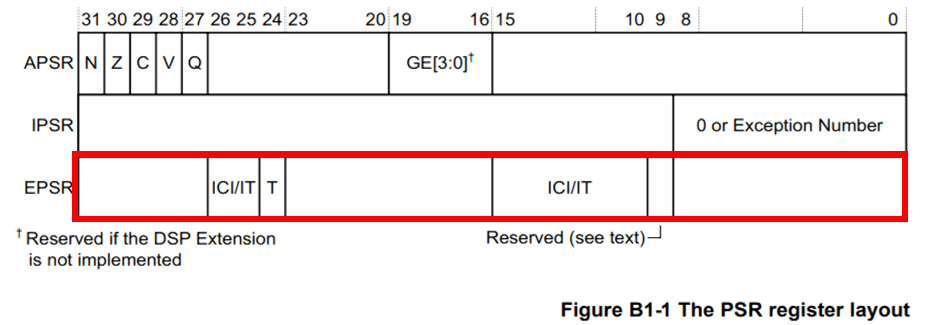

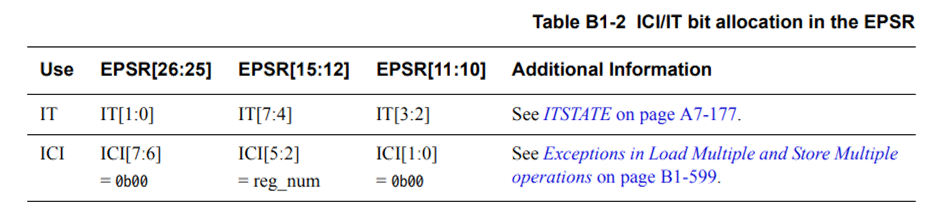

· ICI/IT,bits[26:25], bits[15:10]

EPSR의 [26:25], [15:10]을 보시게 되면 ICI/IT 두개의 Overlapping Fields가 보이게 되는데 이 부분을 살펴봅시다.

· ICI(Interruptible-Continuable Instruction)

ICI는 Multiple Load나 Multiple Store Instruction(ex. LDM, STM) 실행 중에 interrupt 발생 시,

Multiple Operation의 다음 Register Operand를 저장하는 놈입니다.

Exception이 발생하면 어떤 연속적인 Load나 Store를 하는 중이라 하더라도 Exception을 빨리 처리해줘야합니다.

따라서 연속적인 Load나 Store를 끊고 Exception을 처리하러 가야하는데

Exception을 처리하고 돌아왔을 때 끊긴 부분에서 못다한 Load나 Store를 이어나가야겠죠.

따라서 Exception이 발생했을 때,

Exception을 처리하고 돌아와서 할 Multiple Operation의 다음 Register Operand를 저장한다고 보면 되겠습니다.

이런 Multiple Operation의 다음 Register Operand는 위 Table에서 볼 수 있듯이 EPSR bits[15:12]에 저장됩니다.

· IT(If-Then Instruction)

IT는 If-Then instruction의 실행 상태 비트로 If-Then block에 있는 instruction의 개수와 실행 조건을 포함합니다.

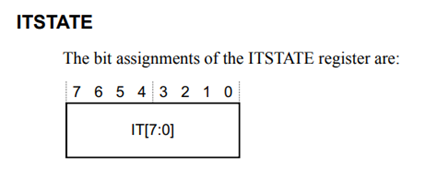

ITSTATE Register의 bit들이 위와 같이 EPSR의 각 bit로 나눠 들어가게 되는데 이 ITSTATE Register에 대해 살펴봅시다.

· IT[7:5] : base condition for the current IT block

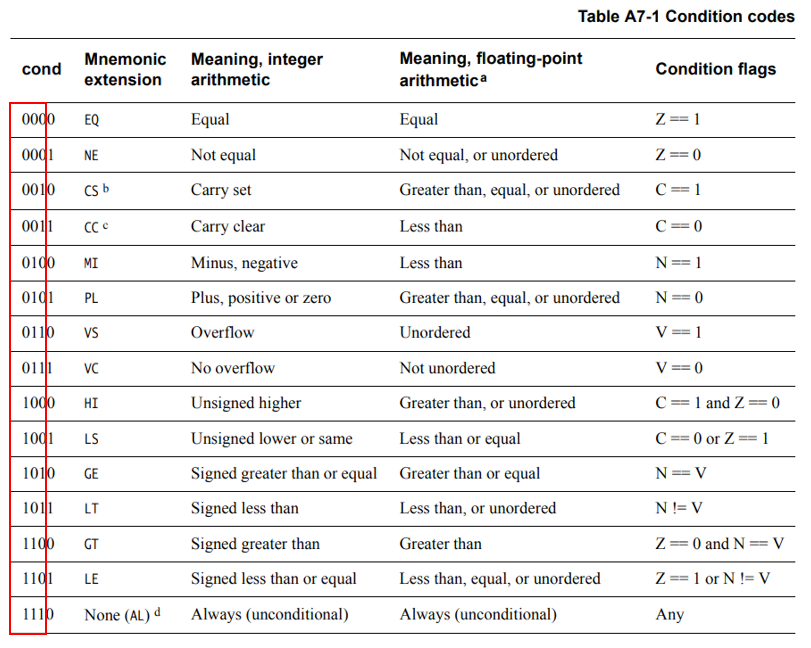

IT의 [7:5]는 base condition이라고 해서 흔히 아는 if문에서의 조건을 의미한다고 보면 됩니다.

예를 들어 if~then, else 문에서 두 값이 같다면(if) ~해라, 다르다면(else) ~해라라고 작성하듯이 말이죠.

이런 3-bit base condition값은 뭐가 있는지는 아래를 참고하세요.

· IT[4:0] : Size of the IT block

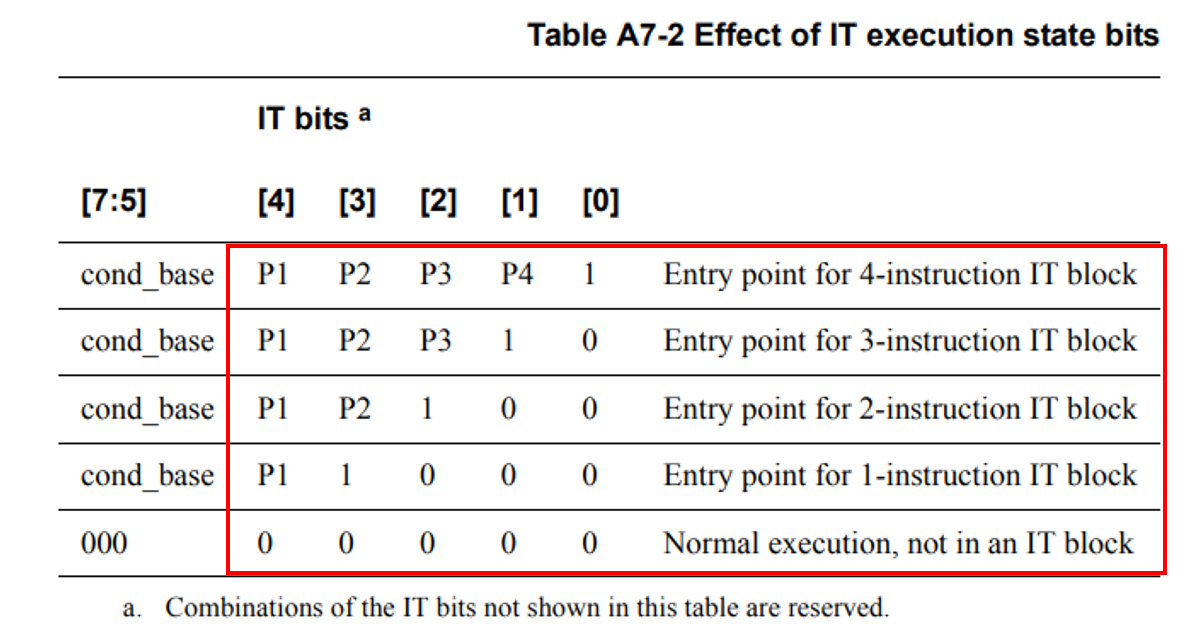

IT의 [4:0]은 IT block의 Size를 나타낸다고 되어 있는데 이것도 마찬가지로 우리가 if~else문을 작성한다고 했을 때

if~then이나 if~then, else로 작성할 수도 있겠지만

if~then, then, else, else 처럼 조건을 만족하거나 다를 때, 여러가지 instruction을 넣을 수 있겠죠.

Cortex-M7은 IT block에 4개의 instruction을 지원해주고 [4:0]은 IT block에 있는 Instruction의 개수를 나타냅니다.

Special Register에 대해 이번 포스트로 다 끝내려고 했는데 예상과 다르게 PSR 설명하는데에도 너무 길어졌네요.

이번 포스트는 여기서 끊고 다음에 이어서 Special Register를 살펴보도록 하겠습니다.

최근댓글