지난 포스트 마지막에서 이야기했듯 AXI Bus의 Read/Write Response Signal에 대해 살펴보지 않고 넘어간 것 같아

이번 포스트에서는 AXI Bus의 Response 부분을 정리해보려고 합니다.

잠시 이전에 배웠던 Bus들의 Response Signal을 떠올려 보면

APB Bus에서는 PSLVERR라는 단순 1-bit짜리 Error Response Signal이 존재했었고

AHB Bus에서는 OKAY,ERROR,SPLIT,RETRY를 포함하는 HRESP라는 2-bit짜리 Response Signal이 존재했었습니다.

AXI Bus도 AHB Bus와 마찬가지로 Read Transfer에 대한 Response Signal인 RRESP,

Write Transfer에 대한 Response Signal인 BRESP라는 2-bit Response Signal이 존재하는데요.

이에 대해서 살펴봅시다.

- RRESP, BRESP

AXI Bus의 경우 위와 같이 OKAY, EXOKAY, SLVERR, DECERR이라는 총 4개의 Response를 가지는 2-bit Response Signal이 존재합니다.

앞에서 말했듯이 RRESP는 Read Transfer에 대한 Response, BRESP는 Write Transfer에 대한 Response인데요.

Write시에는 Write Response Channel이라는 Response를 보내는 Channel을 통해서 BRESP를 보내는 건 알겠는데

Read시에는 어떤 Channel을 통해서 Response가 전달될까요?

Read시에 RRESP는 Read Data Channel을 통해 Response가 전달됩니다.

이유에 대해서 유추해보자면 Response라는 것은 Slave가 Master가 지시한 Transfer가 어떻게 처리되었는지 응답을 하는 것이기 때문에 Slave측에서 Master측으로 가는 Signal이죠.

따라서 Read Transfer 시, 애초에 Slave가 Master에게 Read Data Channel을 통해 Read Data를 보내기 때문에

이때 같이 잘 Read가 되었는지에 대한 Response도 같이 실어서 보내주게 됩니다.

반면 Write Transfer의 경우는 Master가 Slave에게 Write Address나 Write Data를 모두 주는 입장이므로

Master가 Slave로부터 응답을 보고받을 방법이 없기 때문에 Slave에서 Master로의 방향을 가지는

Write Response Channel이 따로 존재하게 되겠네요.

이제 다시 Signal로 돌아와서 하나씩 살펴봅시다.

OKAY는 당연히 Read나 Write가 잘 수행되었다는, 말 그대로 Okay겠습니다.

그런데 비슷하게 생긴 EXOKAY라는 것이 또 존재하네요.

이는 EXclusive OKAY라는 신호인데 이 부분은 아래에서 따로 살펴보도록 합시다.

다음으로 SLVERR, Slave Error입니다.

PSLVERR에서도 살펴봤던 것이라 낯설지가 않네요 :)

설명을 읽어보시면 해당 Slave에 대한 Access는 정상적으로 이루어졌지만 Slave가 어떤 이유에서인지 Error상황을 표출하기 위해서 해당 Signal이 사용된다고 하네요.

마지막으로는 DECERR, Decode Error입니다.

이 Signal은 Read나 Write를 하려고 Address를 보냈는데 해당 Address에 Access할 Slave가 없는 상황일 때 나타납니다.

즉, 단순히 말하자면 주소가 잘못된 상황에 해당 Response가 나타나게 됩니다.

- Exclusvie OKAY

마지막으로 앞에서 설명하지 않았던 EXOKAY Response에 대해 봅시다.

EXOKAY Response를 설명하기 위해서는 Exclusive Access라는 것을 먼저 살펴봐야하기에 미뤘었는데요.

Exclusive Access란 독점 Access라는 의미입니다.

이 의미를 살펴보기 위해서 아래와 같이 Bus 상에 여러개의 Master가 존재하는 상황을 살펴봅시다.

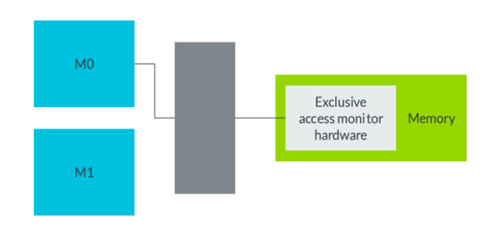

Bus상에 여러개의 Master(M0, M1)가 있고 어떤 Master든 접근할 수 있는 Memory 하나가 있는 상황입니다.

이때, M0가 이러한 공유 자원인 Memory에 독점적으로 Read/Write를 하고 싶은데 이럴 때 Exclusive Access를 시도할 수 있습니다.

단, 중요한 점은 독점 Access(Exclusive Access)라고 해서 다른 Master들이 해당 Memory에 접근할 수 없도록 막는 것이 아니라는 점입니다.

음,,? 천천히 살펴봅시다.

M0가 Memory에 독점적으로 접근을 해서 Memory에 있는 Data를 수정하고 싶은 상황이라고 또 하나 가정해볼게요.

이때 Memory 내용을 바로 Write해서 수정할 수 있을까요?

아니죠.

다른 포스트나 Cortex 포스트에서 설명했듯 CPU는 Read-Modify-Write가 기본입니다.

즉, 수정하고 싶은 주소의 Data를 Read해오고, 수정(Modify)을 해서, 다시 Memory에 Write를 해야한다는 것이죠.

따라서 M0가 Exclusive Access를 통해 Memory 내용을 수정하고 싶다면

Exclusive Read를 한 뒤 수정(Modify)을 해서 다시 Write를 해야합니다.

그런데 앞서 Exclusive Access는 다른 Master들이 해당 Memory에 Access하는 걸 막는게 아니라고 했습니다.

즉, M0가 Exclusive Read-Modify-Write 하는 도중에 다른 Master가 Memory에 접근해서 Data를 수정해버릴 수도 있다는 것입니다. 그러면 M0는 Exclusive Access를 실패한게 되겠네요.

이때는 해당 Exclusive Access가 취소되고 나중에 다시 Exclusive Access를 시도하게 됩니다.

반대로 Exclusive Read-Modify-Write 하는 도중에 다른 Master가 Memory에 접근하지 않았다면 Exclusive Access 성공이겠고요.

다시말하면 Exclusive Access는 한 Master가 독점 Access를 시작하고 끝날 때까지 다른 Master가 끼어들어오는지 확인을 하는 것이지 막는 것은 아니라는 겁니다.

그럼 그냥 다른 Master의 Access를 막아버리면 독점 Access가 실패할 일도 없고 좋은데

왜 굳이 이런 Exclusive Access를 사용할까요?

다른 Master의 Access를 막아버리는 Locked Access도 물론 존재합니다.

하지만 이렇게 Lock을 해버리면 공유자원을 완전히 점유해버리면서 그 공유자원에 접근하고자하는Master들은 모두 대기에 걸릴테고 그렇다 보면 Bus Performance에도 좋지 않은 영향이 가게되기 때문에

위와 같이 공유자원을 Lock하는 것이 아닌 Exclusive Access를 사용하는 것입니다.

EXOKAY를 설명하려다 Exclusive Access에 대한 설명이 길어졌네요 :)

Exclusive Access를 알았다면 이와 관련한 Response Signal인 EXOKAY는 단순합니다.

EXOKAY는 Exclusive Access가 성공했음을 알리는 Response입니다.

즉, 한 Master가 공유자원에 대해 Exclusive Access를 시도하는 동안 다른 Master가 해당 공유자원에 Access하지 않았을 때 EXOKAY Response가 나타나게 됩니다.

반대로 실패했을 경우, 즉 한 Master가 공유자원에 대해 Exclusive Access를 시도하는 동안 다른 Master가 해당 공유자원에 Access했을 경우네는 OKAY Response가 나타나게 됩니다.

이렇게 AXI Bus에 Response Signal에 대한 정리를 마지막으로 AXI Bus Protocol에 대한 포스트는 마치도록 하겠습니다.

최근댓글