이번 포스트에서는 APB Bus에 이어 AHB Bus에 대해 알아보도록 할게요.

일전에 말했듯 Performance보다는 최적화에 초점을 맞춘 APB와 달리 AHB는 보다 Performance에 집중한 Bus입니다.

즉, AHB Bus는 High-Performance 설계의 요구사항을 해결하기 위한 차세대 AMBA BUS로

Burst Transfer과 같은 High-Performance, High Clock Frequency Systems에 필요한 기능을 구현해놨죠.

그럼 ARM사의 AMBA AHB Protocol Specification을 보면서 한번 공부해보겠습니다.

- Bus System

문서에 가장 먼저 나오는 부분은 Bus System이 어떻게 이루어지는가 입니다.

이건 APB Bus에 대해서 공부할 때도 나왔던 내용인데요.

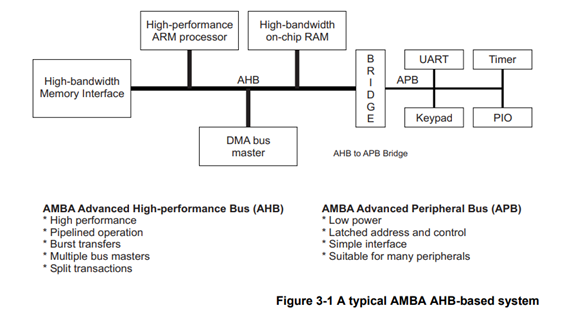

보통 AHB, APB 하나에 전체 IP를 묶어서 쓰지 않고 고속 기기들은 고속 Bus인 AHB에, 저속 기기들은 저속 Bus인 APB에 묶고 Bridge로 Bus를 연결해서 사용합니다.

이건 한번 봤던 내용이기도 하고 Bus를 각각 분리해서 Bridge로 엮어서 사용한다 정도로 알고 넘어갑시다!

- Master, Slave, Arbiter

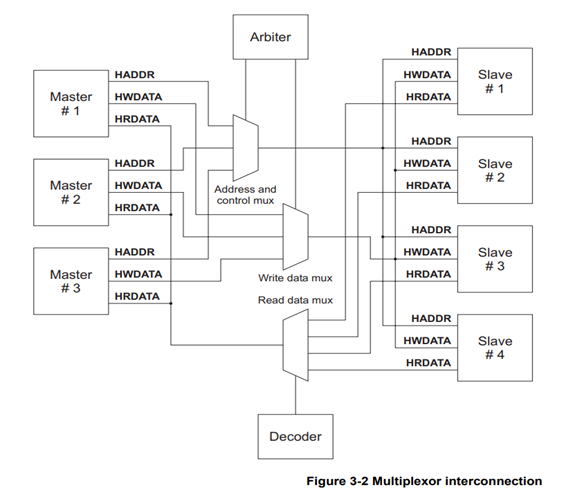

AHB Bus에는 APB와 달리 Arbiter라는 놈이 등장합니다. 아래를 보실까요?

위 그림에서 Master가 총 3개, Slave가 총 4개가 보입니다.

Master와 Slave는 APB를 공부하면서 봤으니 뭔지 알겠는데 Arbiter라는 것이 MUX Select Singal와 연결되어 있네요.

이건 뭘까요?

먼저, Arbiter는 직역하면 "중재자"입니다.

위와 같이 여러개의 Master가 있는 상황에서 Transfer를 하기위해 Bus를 점유하는 Master는 단 하나여야 합니다.

예를 들어 Master#1이 Bus를 통해 Read/Write를 하고 있으면 다른 Master#2, #3는 Bus를 쓰고 싶어도 쓰지 못한다는 이야기입니다.

그러면 여러 Master가 Bus를 전부 쓰고 싶어하면 누구한테 Bus 점유권을 줘야할까요?

바로 이렇게 여러 Master가 Bus를 사용하고 싶어할 때, 우선순위에 따라 "중재"를 해주는 것이 Arbiter입니다.

이런 상황에서 Arbiter는 어떤 Master가 Bus를 점유할지 결정해줍니다.

어떻게?! 궁금하지만 자세한 Arbitration 과정에 대해서는 차차 알아보도록 하고

여기서는 Arbiter라는 놈이 뭐하는 녀석인지 파악만 하고 넘어갑시다.

- AHB Signals

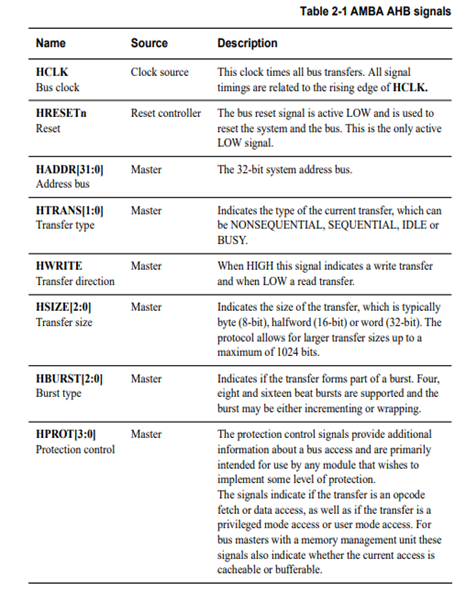

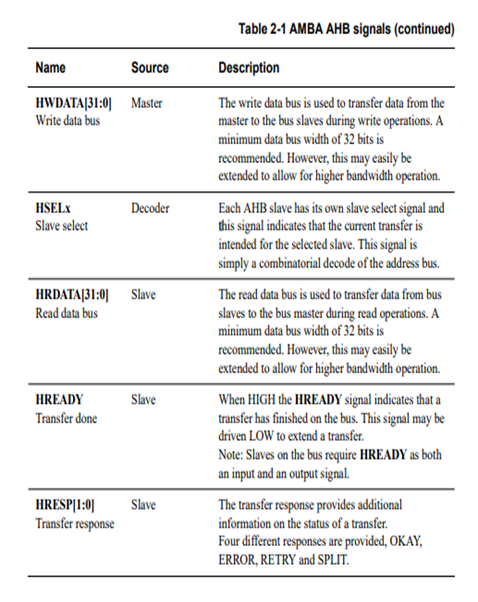

그럼 이제 AHB Bus에 대한 Signal을 알아봐야겠죠.

음 APB Bus에서 봤던 익숙한 Signal들도 보이고 생소한 Signal들도 보입니다.

APB와 다른 AHB Signal들을 살펴보자면 HTRANS[1:0], HSIZE[2:0], HBURST[2:0], HPROT[3:0] 정도가 있는 것 같네요.

AHB Signal들에 대해서는 표를 참고하시고 저는 Burst Transfer에 대해 공부하면서 Signal들에 대해 알아가보도록 하겠습니다.

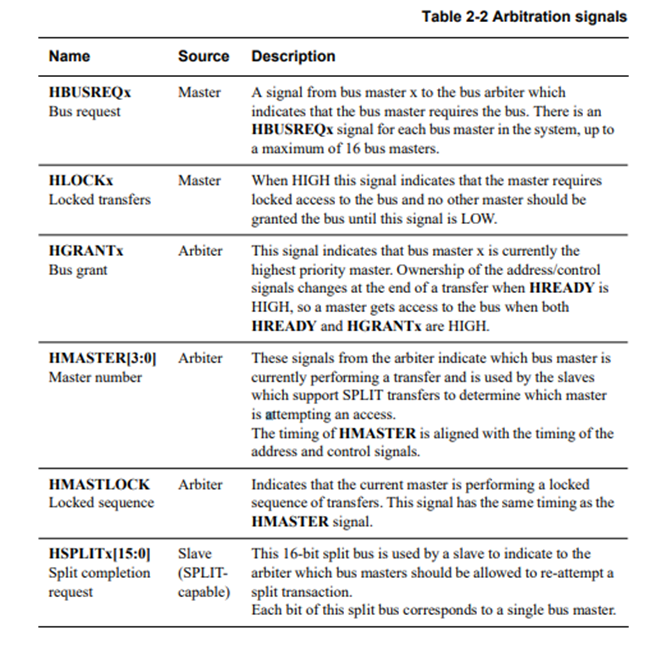

추가적으로 위의 Signal들이 바로 AHB Bus에 있는 Arbitration Signal입니다.

이 또한 표를 참고하시고 이후 Arbitration 과정에 대해 살펴보면서 Arbitration Signal들에 대해서도 살펴보도록 할게요.

- Single Transfer

먼저, AHB Bus의 Single Transfer에 대해서 살펴봅시다.

AHB Bus의 Single Transfer는 APB Bus와 거의 흡사합니다.

차이점이 있다면 APB에서는 IDLE, SETUP, ACCESS State로 총 3가지의 State가 존재했지만

AHB에서는 Address, Data Phase로 총 2가지의 Phase가 존재합니다.

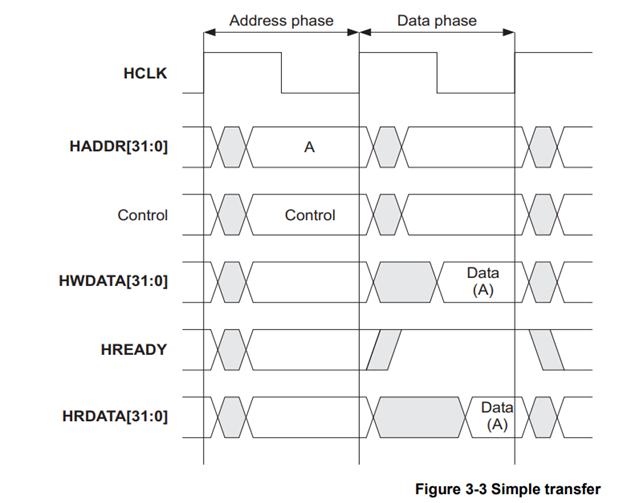

각 Phase에 어떤 일들이 일어나는지 간단히 살펴보면

AHB Bus에서는 어떤 Transfer가 이뤄질 때, Address Phase에서 Address와 Control Signal들이 Set되고

Data Phase에서는 Data들이 Drive되게 됩니다.

즉, Address Phase에서 Read/Write를 할 Address와 HSEL, HWRITE와 같은 Control Signal들을 Set하고나면

Data Phase에서 실제 Read/Write Data가 Bus를 통해 Transfer되는 것입니다.

Single Transfer만 봤을 때는 APB Bus와 상당히 유사하고 이렇게만 본다면 APB랑 뭔 차이인가 싶은데

AHB Bus에서 중요한 점은 앞서 설명한 Address Phase와 Data Phase가 중첩이 된다는 점과

이를 통해서 Multiple Transfer를 할 수 있다는 점입니다.

- Multiple Transfer

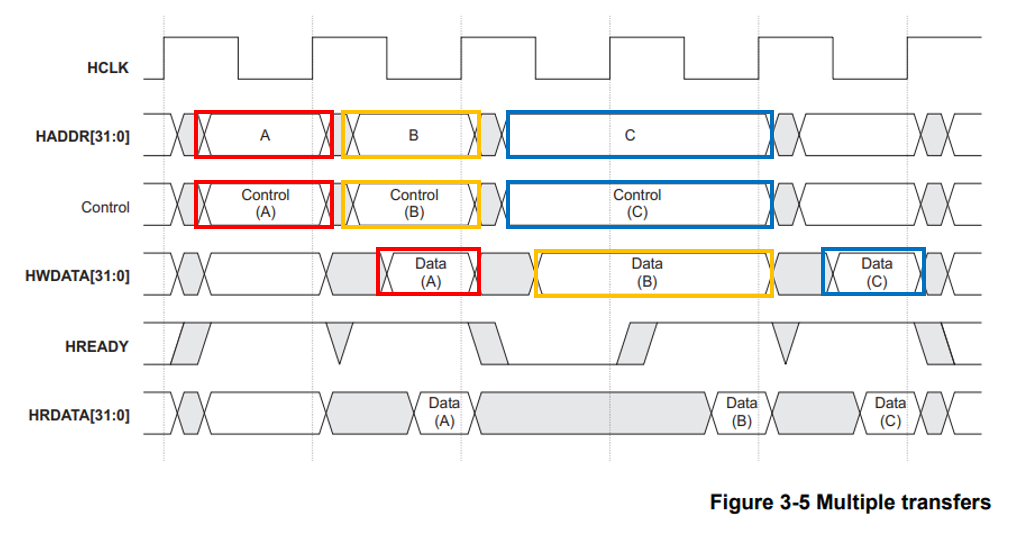

파형을 살펴보시게 되면 첫번째에 A의 Address Phase가 나왔으니 다음에 A의 Data Phase가 나와야하겠죠.

근데 A의 Data Phase 구간에 B의 Address Phase가 동시에 나타나네요.

이것이 AHB Bus의 대표적인 특징인 Address Phase와 Data Phase의 중첩입니다.

이런 중첩을 보기 쉽게 나타내려고 하나의 Transfer의 Address Phase, Data Phase를 같은 색으로 정리를 해봤어요 :)

이렇게 Address Phase와 Data Phase를 중첩함으로써 여러 Transfer가 주루룩 이루어지는 Multiple Transfer를 구현할 수 있겠죠.

당연히 이런 Multiple Transfer를 통해 High-Performance를 이뤄낼 수 있을테고요.

음,, 이후에 내용이 살짝 방대해질 거 같아 이번 포스트는 AHB Bus에 대한 Intro 정도로 마치도록 결정했어요.

자세한 동작과 Signal들에 대해서는 다음 포스트를 참고해주세요 :)

최근댓글